This is a tutorial for how to run a VHDL program on Xilinx. Here we are checking the output in the form of Test bench waveform. The VHDL program which we used in this tutorial is AND gate program.

1) Open XILINX. You will find the below window

2) Click on File => New project. The below window will be open

3) Type the project name and click on next to get below window.

4) Click on Next and you will find this window.

5) Click on New Source and then new source window ill be open.

6) Click on VHDL Module and then enter the File name. File name should be matched with your project name. After that click on Next. See the below window.

7) Then insert the inputs and outputs in the above window. If you want to add input then in Direction column select in while for output terminal select out. Enter the port names in the Port name section. If your input or output is having 8 bit. Let's say i have an input called y which I want to declare as (7 downto 0) i.e. 8 bit. Then mark the box in the Bus column.You will find 0 is there in MSB and LSB section. Now enter 7 in the MSB section while 0 in the LSB section so that we will get (7 downto 0) input. We are executing a simple AND gate program. So here a and b are my input's while c is the output. See the below window.

8) Click on Next and then finish.then you will get the window we get in step 4 as below.

9) Click on next.Then in the new window again click on next. In the next window click on Finish.You will get the program window.

10) As you can see the entity of the program is already generated. You just have to enter the program inside architecture body. We are executing a simple AND gate program. You can enter your own program. See below window.

11) Now see to the left hand side.There you will find Implement design option. Expand it to get check syntax shown in the below window by red rectangle.

12) Click on check syntax. If there is no error in the program then it will show a green mark like in below picture. After this right click on the part shown by red rectangle in the below picture. Select New source option from it.

13) New source window will be open as below.

14) Select the Test Bench waveform and enter the File name. File name should be other than project name. For example here I will enter the File name as firstprogram_tbw. Then click on Next. In the next window click on Next and then finish. Now Initial clock timing and clock wizard window will be open.

15) Since our project of AND gate doesn't contain any clock we will select combinatorial clock option. If your project has clock then select single or multiple clock depending on the no. of clocks used in your program.

16) Click on Finish and you will find below window.

17) Apply conditions by clicking on the blue portion. A lower line indicates logic 0 while a higher line indicates logic 1. Save it by pressing ctrl+s .

18) Close the window of waveform i.e. Close the firstprogram_tbw.tbw window. Now on the left hand side make some changes. First in the sources section change the option of ' Sources for : ' from Synthesis/implementation to behavioral simulation as shown by the red rectangle in the below window. After that click on the part shown by Blue rectangle. In the processes section.You will find XIlinx ISE Simulator option expand it till the last. and click on the generate option.

19) After generation you will find the below window. Now Expand the Xilinx ISE Simulator as shown in the below diagram. Click on simulate behavioral model.

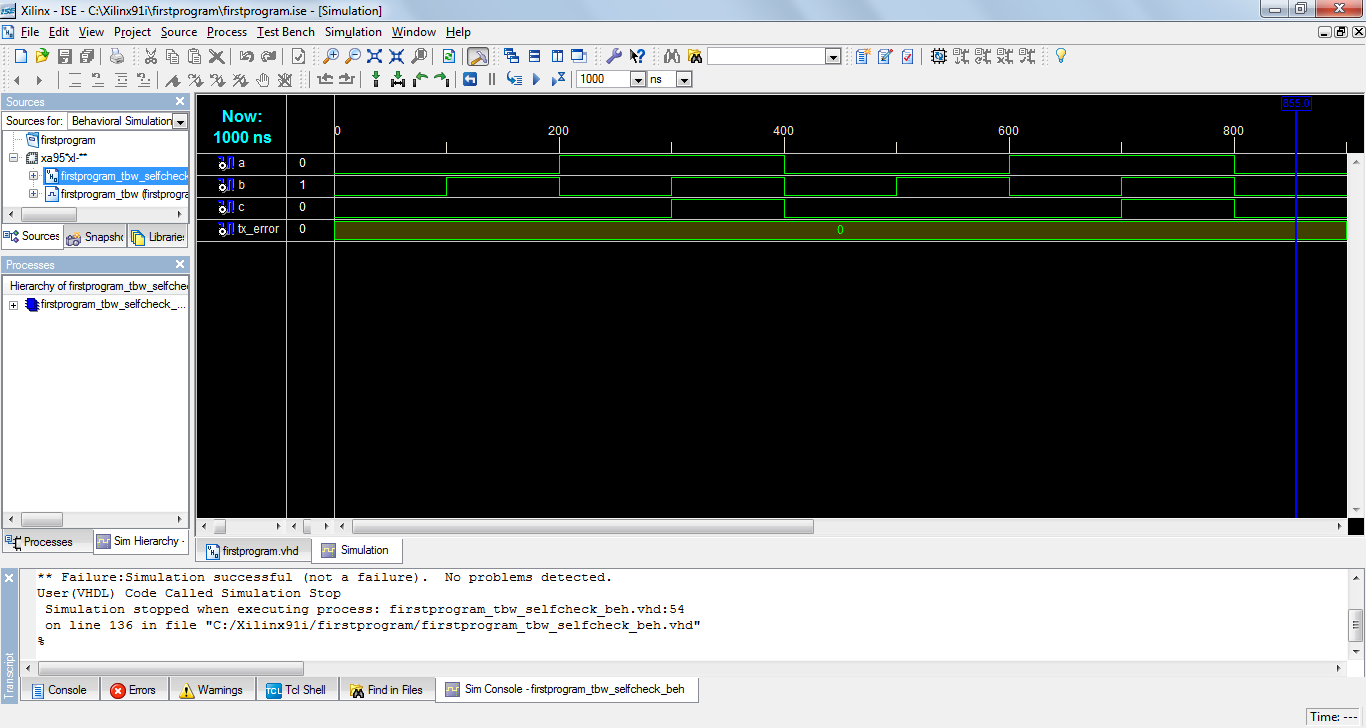

20) After that you will find your output waveform as below.